## PCI Decommutator/Simulator Card

- PCI-based Data Decommutation

- · Data Rates from 10 bps to 10 Mbps

- Support for Multiple PCM Streams

- 8 to 16 bit Word Length

- · Accepts TTL or RS-422 inputs

- IRIG A, B, & G Time Input

- · Onboard Minor Frame Time Tag

- Supports IRIG Chapter 8 1553 Data

- Supports embedded PCM Frame/Asynchronous Blocks

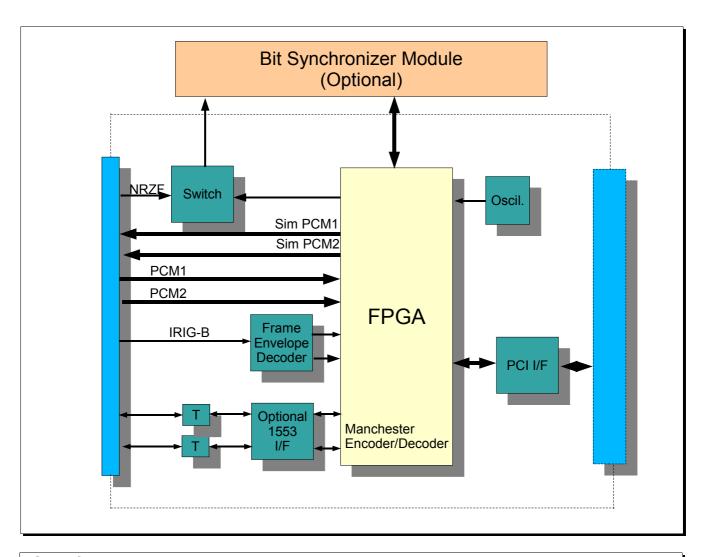

The TMC-10127-01 is a complete ¾ length PCM Telemetry Card for the PCI bus. It contains two PCM decommutator (NRZ-L and B.R) via RS-422 differential receivers or an analog PCM input data stream using an optional Bit synchronizer (\*) piggy-back card, IRIG time code reader and two channels PCM simulator. Each decommutator selects one input PCM channel for decommutation out of 3 available: (Output of the Bit synchronizer or differential PCM input or single ended PCM input). The simulator features dynamic counter and unique data words generation. The time code reader accepts IRIG B time code and can be programmed to utilize system time in the absence of an IRIG time source. It has a DMA engine to facilitate high-speed data transfers across the PCI bus. Setup parameters for each function are programmed via the PCI bus. Read back (status) is available over the same bus in a status word.

The TMC10127-01 card is fully supported by the PLR IDE software package thus providing all the required control such as: Setup, PCM streams recording and playback, real time display, data base management including calibration and scaling, reports preparation and generation and various search functions.

The TMC10127-01 card also includes an optional MUX-BUS 1553B monitor or R/T interface and two analog MANCHESTER – 50-Ohm single ended interfaces.

\* Lumistar LS-040, SBS 4400-TF

## Specifications:

• PC Interface: 3/4 size standard PCI, Rev. 2.1

Bit Rate: 250 bps to 10 Mbps

Word Length: 8 to 16 bits.

Minor Frame Length: Up to 16384 Bits per Minor Frame

Bit Order: MSB-first.

• Frame Sync Pattern: Up to 32 bits. Any combination of 0, 1. any bit can be Don't Care bits.

Sync Strategy: Adaptive Mode: (Search<—>Verify<—>Lock).

Sync Error Tolerance: none.

PCM Simulator:

Data Polarity: Normal, Inverted.

Major Frame Length: Up to 256 frames

Subframe Sync: SFID (count up/down).

• SFID Location: Any contiguous bits on a PCM word boundary in minor Frame.

External Time: Input format: IRIG B, with flywheel optional

Carrier: 1 KHz Input Level: 1 – 5 V p-p

Outputs: Automatic Time Tags for PCM data blocks

Output Codes: PCM Output codes NRZ-L, RNRZ-15

Bit Rate: 250 bps-10 Mbps NRZ codes. 5 Mbps for other codes

Word Length: 8 to 16 bits Transmission Order:MSB first.

Minor Frame Length: Up to 16384 Bits per Minor Frame

Frame Sync Pattern: Up to 32 consecutive bits may be declared as sync.

Frame sync pattern must begin and end on word boundaries.